近日,南边科技年夜学深港微电子学院副院长余浩传授的《智能感知的边沿计较芯片的研究进展与成长趋向》被CCF2020-2021中国计较机科学技能成长陈诉采录。这是CCF学术事情委员会挑选出的具备代表性的14篇高程度陈诉之一。

中国计较机学会(CCF)是天下一级学会,自力社团法人,中国科学技能协会成员,是中国计较机和相干范畴最有影响的学术集体。CCF年度中国计较机科学技能成长陈诉为CCF很是主要的年度总结陈诉,包罗系统布局、计较机视觉、理论计较机科学、信息体系、收集与数据通讯等标的目的的陈诉,从碳中及系统布局、视觉-语言交互技能、生物信息学组合优化、新一代常识图谱信息体系、Sketch驱动的收集丈量等多角度论述了不停立异的主题,具体先容了响应研究标的目的的近况、海内研究进展、海内外研究进展对于比、成长趋向以和各自的立异看法等。

《智能感知的边沿计较芯片的研究进展与成长趋向》从当前边沿计较芯片研究的三个基本问题:感算共融架构的一体化处置惩罚问题、深度神经收集的简化优化问题与深度神经收集加快器架构低能效问题入手举行论述,总结最近几年来海内皮毛关研究进展,并对于海内外研究近况举行阐发与比力,针对于今朝业内可行性标的目的给出成长趋向的总结与瞻望。

1. 感算共融架构的一体化处置惩罚问题:针对于感知及计较的分立设计方案存于的输出及数据转换接口价钱,海内外提出多种感算共融智能架构,包括多维度可扩大的“传感-计较”体系,高能效“传感+存算一体”混淆旌旗灯号集成实现。而且针对于共融架构,面向硬件部署的算法优化、容错架构设计、模仿电路靠得住性设计及感知校准要领需要深切切磋从而解决混淆旌旗灯号共融架谈判电路的多种非抱负因素,晋升低功耗智能芯片的机能及靠得住性;

2.深度神经收集的简化优化问题:于很多呆板进修的运用场景中,深度神经收集的部署遭到延迟、能量耗损及模子巨细的约束,尤其是于一些计较能力相对于较弱的边沿装备上。为相识决这个问题,海内外提出多种针对于在神经收集压缩及加快的要领,包括神经收集剪枝,权重矩阵低秩分化,权重量化等。而且最新研究趋向是基在面向收集架构主动优化(NAS)的优化方案,经由过程对于自界说搜刮空间内的收集布局及超参数举行寻优,使患上主动天生的收集模子比人工设计的模子机能更佳;

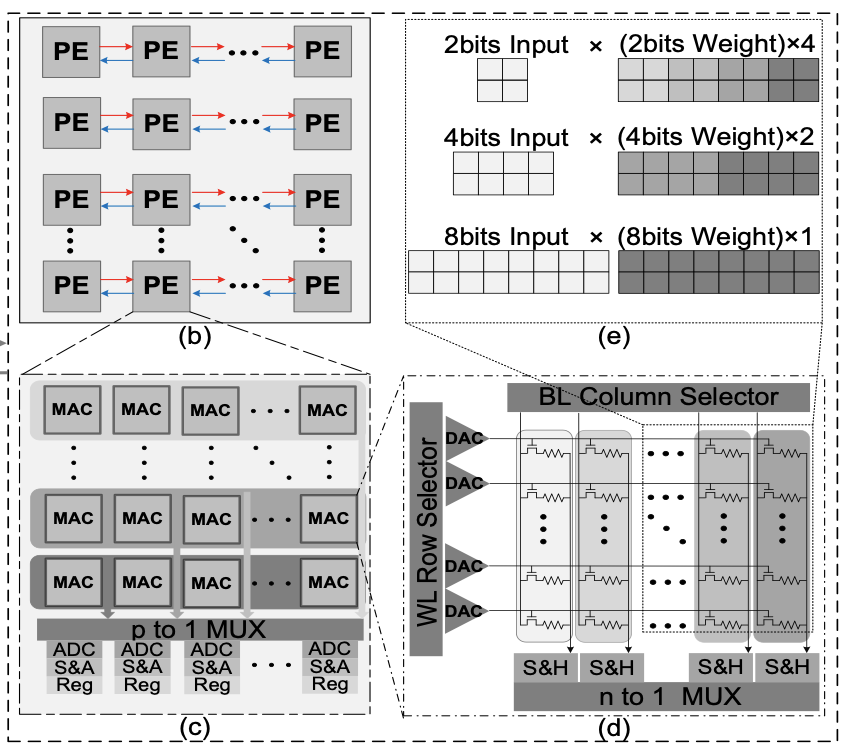

3. 深度神经收集加快器架构低能效问题:CNN中构成部门是卷积(conv)层及全毗连(FC)层,于练习及推理历程中,这两个层重要需要的运算操作是乘加运算及数据存取,这些运算操作决议了硬件耗损及延迟。为了实现芯片的高通量及低能耗,海内外研究经由过程数据流优化,体系架谈判多精度撑持等方面提出可行性方案。数据流方案中经由过程多种数据复用方式,包括权反复用、输入复用及输出复用等,按照差别收集的特征选用差别的复用方式举行数据流的功耗优化及通量晋升;于体系架构方面,特定在AI的计较体系(即AI加快器)凡是由年夜量高度并行的计较及存储单位组成这些单位以二维方式构造,以撑持神经收集相干运算,片上彀络(NoC)、脉动阵列、张量运算单位以和存内计较等方案别离从收集适配、数据复用及降低数据传输延迟功耗等标的目的对于加快器举行定制化机能优化;于多精度撑持方面,为了撑持逐层比特优化的神经收集,今朝已经经有多种采用串行累加,并行组合以和一体化运算等方案,从运算单位或者阵列体系的角度举行多精度运算撑持,从而实现软硬件的协同优化设计。

文章也给出了深度神经收集加快器架构将来成长标的目的。跟着收集模子的繁杂度增长,对于在芯片计较能力的要求愈来愈高,CPU/GPU的通用性虽然更好,可是其计较效率低下。今朝专用在深度神经收集处置惩罚的芯片虽然计较效率上更有上风,可是其通用性不敷强,是以,于将来的人工智能芯片设计的成长上,可重构智能将会是一个主要的趋向。因为于处置惩罚深度神经收集的历程中需要年夜量的数据搬移,传统的冯诺依曼架构“内存墙”的问题日趋凸起,是以将来存算一体也将会是智能芯片设计的一年夜趋向。于国度“十四五”计划纲要中,于增强原创性引领性科技攻关方面,“进步前辈存储技能”被列入“科技前沿范畴公关”重点范畴。传统存储器邻域,进步前辈技能持久把握于美国,韩国及日本等国度;而于ReRAM等新型存储器的成长上,中国在其他国度站于统一起跑线上,有时机降生下一海力士及美光。

图. 基在收集架构主动搜刮的多精度存算一体感知加快器

-米兰milan