近日,南边科技年夜学工学院国度树模性微电子学院潘权团队于高速通讯与光电集成电路设计范畴取患上进展,研究结果有六款芯片,包括一款PAM-4发射机芯片、一款PAM-4低掉真VCSEL发射机、一款单端PAM-4收发器前端芯片、一款PAM-4单端吸收机前端芯片、一款时钟发生器芯片以和一款无电感光吸收机芯片,前两款芯片的相干论文结果发表在IEEE Journal of Solid-State Circuits(JSSC),第三款与第四款芯片结果发表在IEEE Transactions on Circuits and Systems I: Regular Papers(TCAS-I),第五款芯片结果发表在IEEE Custom Integrated Circuits Conference(CICC),第六款芯片结果发表在European Solid-State Electronics Research Conference(ESSERC)。JSSC与TCAS-I为集成电路设计范畴公认的国际顶级学术期刊,CICC与ESSERC则为该范畴具备主要影响力的国际顶级学术集会,充实揭示了潘权团队于高速模仿/混淆旌旗灯号与光电芯片标的目的的前沿研究实力与国际影响力。

具边缘加强脉冲天生与非对于称前馈平衡的128 Gb/s PAM-4发射机芯片

于云计较及人工智能运用中,需要高机能数据中央来处置惩罚及互换海量数据。这类不停增加的吞吐量需求鞭策了高数据速度的有线发射机的成长。

最近几年来,有线发射机采用PAM-4信令,实现了跨越100Gb/s的数据速度。然而,因为PAM-4信令的中间眼睛及顶部/底部眼睛之间的边沿过渡时间差别,PAM-4信令的眼图体现出不等的转换沿抖动,致使程度眼睛伸开度降低及旌旗灯号完备性恶化。针对于该问题,这项事情提出了一种128Gb/s四电平调制的有线发射机来减轻该旌旗灯号完备性问题。所提出的预加剧非对于称分数距离前馈平衡器处置惩罚了PAM-4眼图中的不等的转换沿抖动,并实现了程度眼宽的拓展。此外,还有采用了分外的5抽头单元距离前馈平衡器来提高平衡器的精度。于发射器输出驱动级中,提出的边沿晋升脉冲发生器提高了带宽,从而加速了TX输出旌旗灯号的边沿转换速率。于串化链路中,使用锁存最小化串行器来优化了数据路径的功耗及面积。

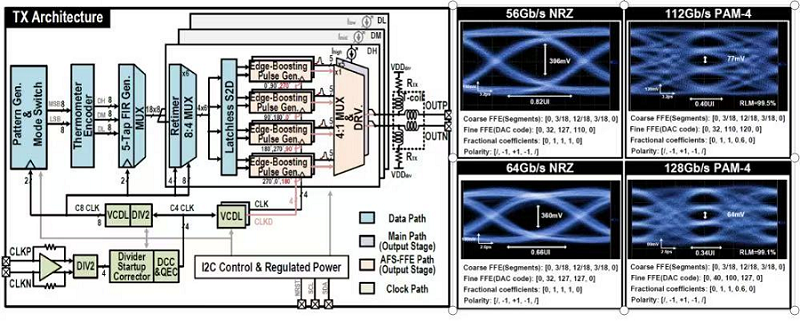

论文[1] 图1(a) 发射机芯片架构图, (b) 芯片测试成果

(a) (b)

论文[1] 图2(a) 芯片照片, (b)芯片功耗漫衍

图1(a)展示了发射机芯片的电路架构图,图1(b)展示了芯片的测试成果。该发射性能够以高达128Gb/s的数据速度举行事情,其能效仅为1.5pJ/b。图2(a),(b)展示了提出的发射机芯片的面积和其功耗漫衍。

2022级博士生吴泓志是论文的第一作者,深港微电子学院潘权传授为论文的通信作者,该论文获得了国度重点研发规划、深圳市科技庞大专项以和广东省重点范畴研发规划经费的撑持。

[1]H. Wu et al.,“A 128-Gb/s PAM-4 Transmitter With Edge-Boosting Pulse Generator and Pre-Emphasis Asy妹妹etric Fractional-Spaced FFE in 28-nm CMOS,”IEEE Journal of Solid‑State Circuits.

论文链接:https://ieeexplore.ieee.org/abstract/document/10967239

56-Gb/s PAM-4低掉真VCSEL发射机

此事情基在40-nm CMOS工艺实现了一款用在驱动VCSEL的发射机芯片。芯片基在温度计码架构设计,经由过程分段式调治输出至VCSEL的电旌旗灯号的PAM-4子眼的高度、宽度及斜度,赔偿VCSEL的增益非线性、带宽非线性及旌旗灯号沿非对于称相应三个非抱负特征,实现低掉真的56-Gb/s PAM-4光旌旗灯号输出。测试成果显示,本事情提出的分段非线性赔偿方案将56-Gb/s PAM-4输出光旌旗灯号的平均子眼高度/宽度及电平不匹配比(RLM)别离提高了14%/12%,并将PAM-4眼图的程度歪斜度降低了63%。

论文[2] VCSEL发射机的架构图及测试成果

此事情发表在2025年IEEE固态电路期刊(JSSC)及2023年IEEE欧洲固态电路集会(ESSCIRC),第一作者为陈福栈博士,潘权传授及港科年夜俞捷传授为配合通讯作者。[2] F. Chen, C. Zhang, L. Wang, Q. Pan and C. P. Yue, A 56-Gb/s PAM-4 VCSEL Transmitter With Piecewise Compensation Scheme in 40-nm CMOS, IEEE Journal of Solid-State Circuits, Early Access, DOI: 10.1109/JSSC.2025.3552590.论文链接:https://ieeexplore.ieee.org/abstract/document/10960651

一种用在长间隔链路扩大的 112Gb/s 单端 PAM-4 收发器前端

跟着全世界互联网流量的急剧增加,有线收发器(TRXs)需要更高的每一通道数据速度。受无源链路的限定,尤其是毗连器及封装的带宽限定,传统的差分的PAM-4方案可能没法同时统筹长间隔链路及高密度高速传输。高速单端信令方案应运而生,单端信令可以显著提高I/Os的密度,从而有用地降低芯片封装及通讯装备面板的繁杂性。然而,实现多通道单端高速信令传输的设计需要降服许多坚苦:1.高机能单转双(S2D)与双转单(D2S),2.重损赔偿,3.低功耗高密度。本文提出了一种基在130nm SiGe BiCMOS的撑持PAM-4数据的小面积及低功耗的单端 TRX 前端,传输数据速度可达112 Gb/s。此收发机前端基在新型的负电容组织、不合错误称电感赔偿、群延迟掉配校准及电感复用技能,实现了20 dB的高频平衡能力,1.81 pJ/bit的能量效率,以和高机能的D2S-S2D转换,合用在400G以上的长间隔多通道高密扩大模块。

论文[3] 单端高速信令架谈判单端收发前真个道理框图

论文[3] 频域时域的测试成果

南边科技年夜学的2022级博士生罗大军为本论文第一作者,潘权传授为通信作者,南边科技年夜学为论文第一单元。本事情获得了国度天然科学基金、国度重点研发规划的撑持。[3] X. Luo et al.,“A 112-Gb/s Single-Ended PAM-4 Transceiver Front-End for Reach Extension in Long-Reach Link,” IEEE Transactions on Circuits and Systems I: Regular Papers.论文链接:https://ieeexplore.ieee.org/document/11029623

具备串扰消弭及旌旗灯号再使用的2×80 Gb/s PAM-4单端吸收机前端

跟着数据中央的吞吐量连续增加,电气通道速度平均每一3.9年翻一倍,估计于2026年将到达200Gb/s/lane的速度需求。是以,每一条通道的带宽成为体系的机能瓶颈。思量到今朝的封装及工艺限定,这对于通讯体系带来了巨年夜挑战。基在该配景下,于一对于差分线中采用高速单端传输可以于不异数据率下将体系带宽减半或者者于不异的信道带宽下将吞吐量翻倍,同时能实现100%的高引脚效率。然而,高密单端传输会使I/O更易遭到相邻信道串扰的影响,特别是违板链路毗连器中微带线引入的远端串扰。本文提出了一款基在TAS-TIS架构具备串扰消弭及旌旗灯号再使用的2×80 Gb/s PAM-4单端吸收机前端。为了实现更切确的远端串扰消弭,于均衡微分器中提出了一种共模增益一致技能。为了包管高频能量提取效率,于TAS-TIS架构中提出了Gm倍增技能来改善有限电源电压下加法器的带宽,增益及群时延相应。此外,采用基在电流镜的高能效CTLE能提供矫捷的低/中/高频赔偿,终极于一对于具备13 dB@20 GHz及28 dB@ 28GHz单端损耗的信道上以0.83 pJ/b的能效下实现了2×80Gb/s PAM-4以和1.19 pJ/b的能效下实现了2×56Gb/s NRZ的数据率。

论文[4] 违板运用场景及单端吸收机前真个道理框图(上)时域的测试成果(下)

南边科技年夜学的2022级硕士生张阳奕为本论文第一作者,潘权传授为通信作者。本事情获得了国度天然科学基金、国度重点研发规划的撑持。[4] Y. Zhang et al.,“A 2×80 Gb/s Single-Ended TAS-TIS PAM-4 Receiver Front-End With Crosstalk Cancellation and Signal Reutilization in 28-nm CMOS,” IEEE Transactions on Circuits and Systems I: Regular Papers.论文链接:https://ieeexplore.ieee.org/document/11029623

合用在高速互连的混淆注入锁定八相时钟发生器芯片

跟着数据吞吐需求的不停增加,高速、低功耗的有线收发器成为行业研发重点,而高精度宽带多信赖号时钟天生器(MPCG)是实现这一方针的焦点电路。近日,本事情提出一种基在混淆注入锁定的宽带低噪声多相时钟天生器,显著扩大了事情规模并优化了抖动机能。

传统多信赖号注入锁定技能常面对注入精度及锁定规模之间的衡量,特别受限在延迟锁定环(DLL)的事情规模,致使体系于高频前提下易掉锁,限定了多速度收发器的适配性。针对于这一瓶颈,该团队提出“混淆注入锁定(HIL)”方案,经由过程引入快速调谐环(FTL)实现主动模式切换,当DLL没法锁按时,电路主动转入两相注入模式,打破了传统设计中事情规模依靠DLL的限定。

此外,该设计还有立异性引入自顺应掉配赔偿(AMC)技能,解决电压节制延迟链(VCDL)与振荡器(ROSC)于PVT变化下的频率掉配问题,防止因电流纷歧致致使的相位噪声劣化。AMC经由过程赔偿电流调治,有用提高噪声按捺带宽,其机能领先同类方案。

该电路采兼具能效及小型化上风,为将来多速度、高能效的高速有线互连络统提供了主要技能支撑,特别合用在AI计较及高机能办事器等高带宽场景。

(a)

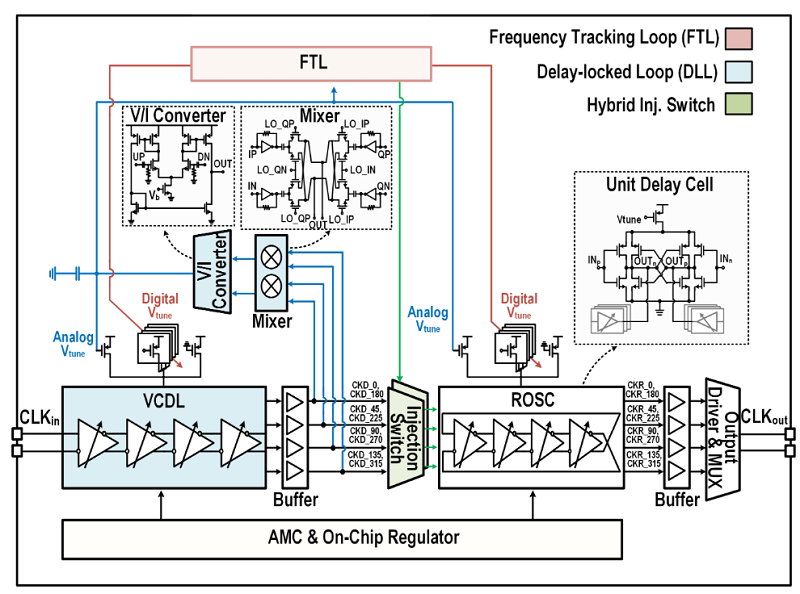

论文[5]图1(a)时钟芯片架构图

(b)

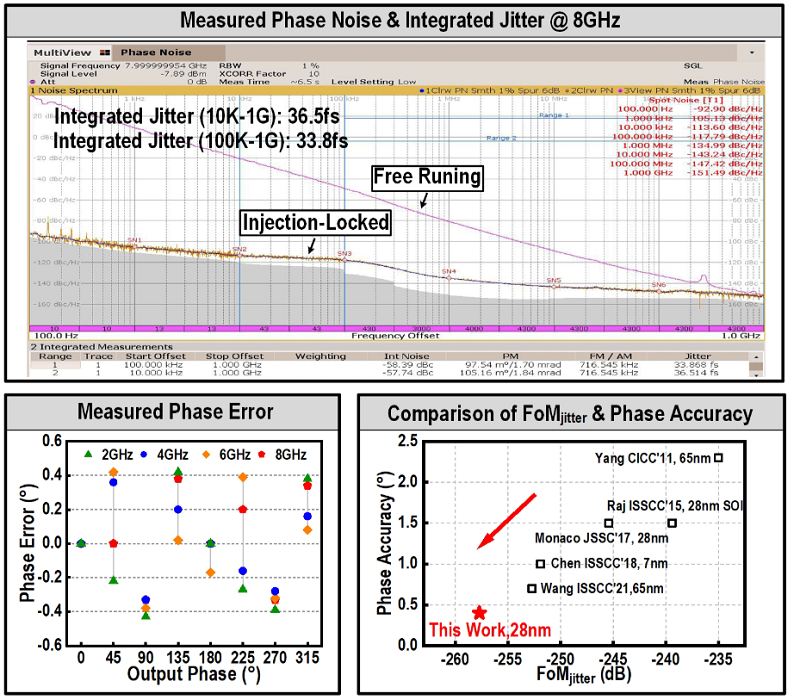

论文[5]图1(b)芯片测试成果

(a) (b)

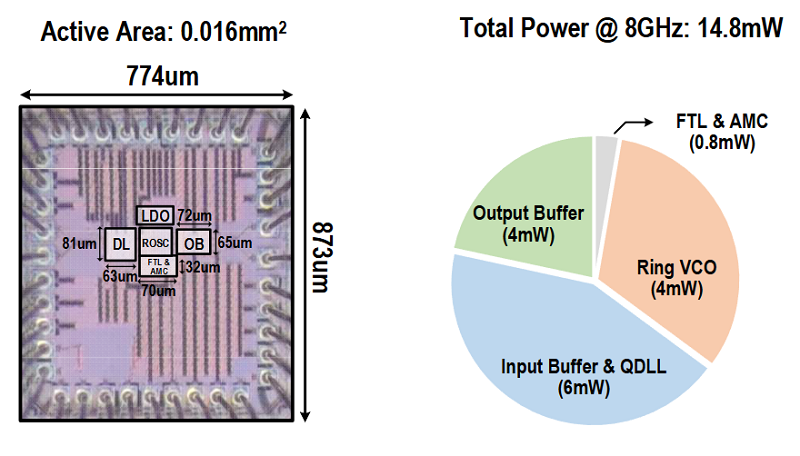

论文[5]图2(a)芯片照片,(b)芯片功耗漫衍

图1(a)展示了时钟芯片的电路架构图,图1(b)展示了芯片的测试成果。该时钟芯片可以或许于0.3-10.1GHz频率规模举行事情,此中8GHz的时钟旌旗灯号输出抖动仅为33.8fsRMS,全频带内的相位偏差小在0.45°,其功耗仅有14.8mW。图2(a),(b)展示了提出的时钟芯片的面积和其功耗漫衍。

2022级博士生吴泓志是论文的第一作者,深港微电子学院潘权传授为论文的通信作者,该论文获得了国度天然科学基金及深圳市科技庞大专项经费的撑持。

[5]H.Wuet al.,“A 0.3-to-10.1 GHz 33.8fsRMS-Jitter Hybrid Injection-Locked Eight-Phase Clock Generator with Adaptive Mismatch Cancellation Technique for High-Speed Links in 28nm CMOS,”IEEE Custom Integrated Circuits Conference.

论文链接:https://ieeexplore.ieee.org/abstract/document/10983468

20-56Gb/s无电感光吸收机

论文[6] 芯片照片(上)

论文[6] 测试情况(下)

论文[6] 光吸收机于56Gb/s速度的误码率

人工智能及呆板进修的快速成长不停晋升了对于数据中央计较能力的需求,基在光旌旗灯号的互联可以实现将几米至几十米间隔的办事器举行毗连,实现漫衍式计较的需求。基在NRZ旌旗灯号的光互连具备低误码率(BER)、低延迟及高带宽密度等上风而备受青睐。然而,为了进一步晋升带宽密度,需要尽可能晋升数据传输的速度及减小芯片的面积。是以,本文提出了一种无电感的光吸收机,实现了面积的最小化;同时,吸收机采用了八分之一速度架构预判式讯断反馈平衡器以进一步晋升吸收机的数据率。该吸收机实现了20–56Gb/s的光速度及20-72Gb/s的电速度,于56Gb/s下到达1.9pJ/b的能效,并具备仅0.019妹妹²的紧凑面积,其数据率与面积于28nm平面工艺下具备显著上风。

南边科技年夜学的2021级博士生程旭旭以和2022级博士生吴泓志为本论文第一作者,潘权传授为通信作者。

团队接待来自海内外顶尖黉舍的学生申请博士后/博士生/硕士生等。

-米兰milan