近日南边科技年夜学深港微电子学院呼喊助理传授课题组于运用在物联网、可穿着体系、下一代生物医疗等多个要害范畴的模仿与混淆旌旗灯号集成电路设计取患上多项主要结果。

论文1: 于运用在物联网超低压下的能量自给电路范畴取患上主要进展,相干结果以论文“A Robust Near-Zero Power Wakeup Timer With a Hybrid Reconfigurable FLL Directly Powered by Uncertain Harvested Voltage Down to 0.3V”[1]被国际顶级学术集会——2024年欧洲固态电子研究集会(European Solid-State Electronics Research Conference, ESSERC 2024)吸收。呼喊助理传授课题组2022级硕士研究生朱宇桐为第一作者,呼喊助理传授为论文的通信作者,南边科技年夜学为论文的第一单元。该结果获得了国度天然科学基金、广东省基础与运用基础研究基金等项目的撑持。

今朝,物联网芯片凡是需要举行传感器感知、数据处置惩罚与传输,而其毫米级的体系体积严峻地限定了电池容量,促使相干芯片设计必需思量体系功耗并到达高能效运作。超低功耗物联网芯片中的绝年夜大都模块于年夜部门时间都处在余暇模式以节省电量。体系的数据处置惩罚与传输模块会按照既定的时钟而被周期性叫醒,是以为了降低功耗并延伸体系的生命周期,需要年夜幅降低叫醒时钟的功耗。传统的叫醒电路凡是采用基在晶体振荡器的及时时钟,然而晶振的物理尺寸严峻限定了其于毫米级体系中的运用。只管最近几年来海内外学术和财产界针对于片上全集成叫醒时钟方面的研究已经经取患了使人瞩目的进展,然而于超低压下的能量自给电路仍旧有许多难点需要霸占。

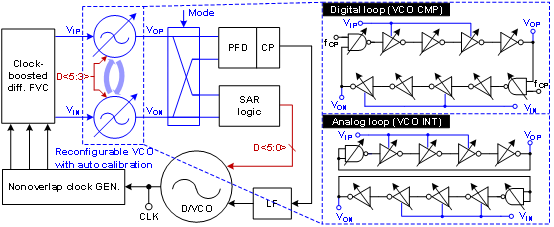

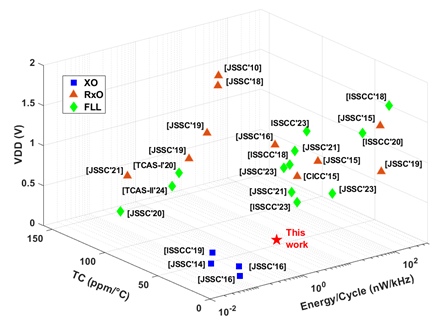

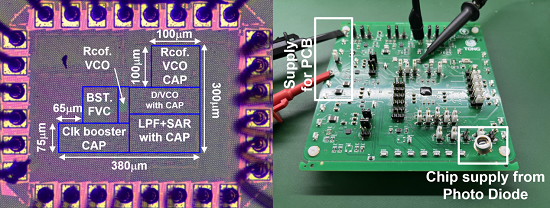

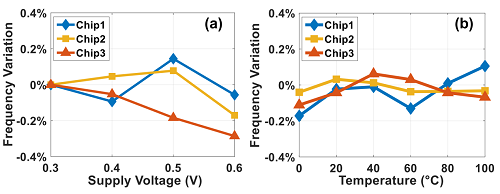

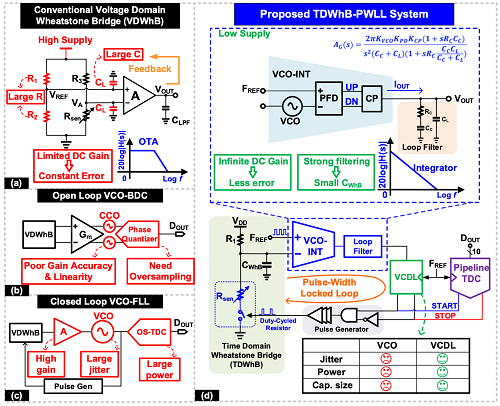

本设计经由过程数模混淆架构解决了超低压下VCO频率规模偏移较年夜的问题,并使其于温度和电压变化时不变输出频率,于模仿和数字回路中经由过程可重构电压检测电路,实现了VCO积分器及边沿追踪比力器的电路复用,如图1所示。本设计解决了超低压下增益不足的问题,并经由过程电路复用减小面积,数字回路的引入使差别电压下VCO均具备不变的增益。图2展示了最近几年来海内外进步前辈时钟架构的机能指标体现,本设计于超低压下到达了靠近片外石英晶振的体现。图3为芯片电镜和电路测试PCB图,实测了仅由外部能量收罗体系供电时芯片的事情状况.该设计可以彻底由片外能量收罗体系供电,实现了全集成化和无电池化。电路测试了由LDO供电时的温度系数和电压系数,如图4所示,这注解时钟芯片具备较高的鲁棒性。

图1:数模混淆叫醒时钟架构(左)和可重构电压检测电路布局(右)

图2:近几年海内外进步前辈时钟架构机能体现

图3:时钟芯片电镜照片,TSMC65nm工艺(左)和测试PCB(右)

图4:(a)27°C时频率随供电电压的变化(b)0.3V时频率随温度的变化

2024年11月18日到21日,IEEE亚洲固态电路集会(IEEE Asian Solid-State Circuits Conference, A-SSCC)于日本广岛市进行。A-SSCC是芯片设计范畴的国际顶级集会之一,旨于展示固态及半导体范畴最新、开始进的芯片及电路设计技能。最近几年来,亚洲列国已经成为集成电路设计、制造及运用发展幅度最年夜的区域。于此配景下,兼具学术与财产影响力的A-SSCC已经成为全世界芯片设计范畴的主要国际集会。这次集会收到343篇投稿,仅录稿125篇高质量论文。呼喊助理传授课题组的两篇论文 “A 1.92nJ/Conv Pulse-Width Locked-Loop Time Domain Readout IC with VCO-Integrator and Pipeline TDC for Wheatstone Bridge Wearable Strain Sensing System”[2]及“An Energy-Efficient Composite Phase Shift 16-QAM Frequency Multiplying TX Achieving a 3.4% EVM in 65nm CMOS”[3]入选了这次集会,论文2的第一作者为南科年夜2019级本科生,哥伦比亚年夜学硕士徐思远,论文3的第一作者为南科年夜2022级硕士研究生罗凯源。呼喊助理传授为两篇论文的通信作者,南边科技年夜学为第一单元。该研究事情获得了国度天然科学基金、广东省基础与运用基础研究基金等项目的撑持。

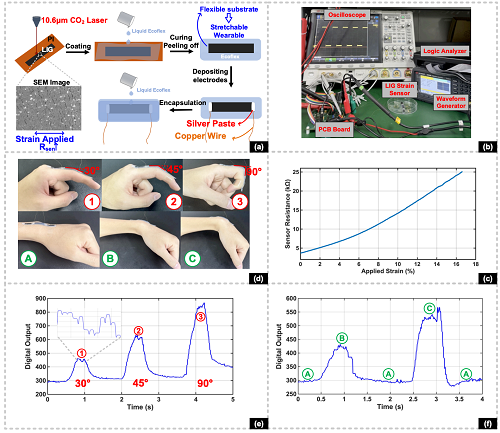

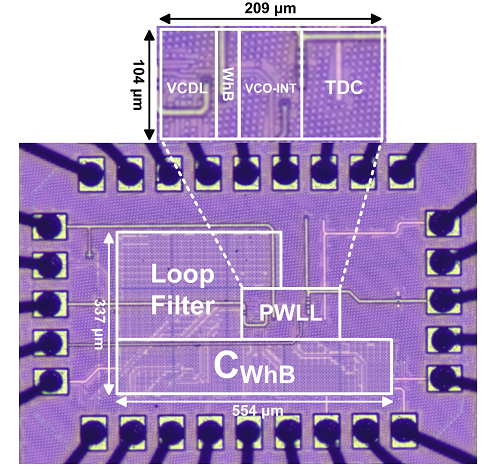

论文2: 最近几年来,柔性可穿着应力传感器于多个范畴有着很年夜的潜于运用价值。该事情提出了一款新型可穿着应力传感读取体系,基在叶怀宇副传授课题组杨荟茹博士制备的激光引诱石墨烯(laser-induced graphene,LIG)高机能应力传感器,设计了一款超低功时域读取电路。该电路提出了一个基在VCO积分器的时域惠斯通电桥架构,相对于在传统的电压域惠斯通电桥有着多方面机能的晋升。该论文还有设计了一款基在延迟比例(Delay Ratio)的Pipeline TDC,以到达更高的能效及更小的面积。该芯片采用65nm CMOS工艺流片,颠末测试该电路实现了很高的线性度(R2 0.99992),仅耗损4.8µW功耗并到达了1.92nJ/conv的能耗效率。

图5:徐思远于集会现场做陈诉

图6:提出的传感器读取体系

图7:应力传感体系测试图

图8:芯片照片

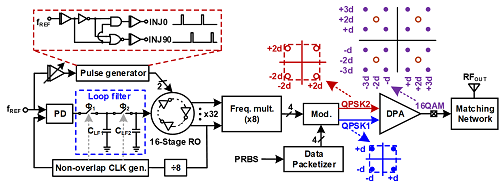

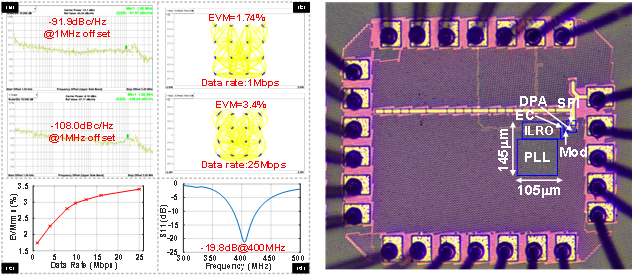

论文3: 下一代生物医疗、可植入人体等物联网装备高度集成化。发射机又往往主导着整个物联网装备的功率开消,是以低功耗,高能效,成了整个发射芯片的庞大挑战。同时部门运用场景如脑机接口,及时图象传输往往对于发射速度提出了更高的需求,比拟在低阶调制体系(OOK/FSK/ASK),QAM等高阶调制发射机凡是可以实现数十Mbps的发射速度及更高的频谱效率。该事情提出了一款基在复合相移法的16QAM超低功耗倍频发射电机路。该电路基在复合相移法设计了一款QPSK旌旗灯号归并的16QAM倍频发射机架构,相对于在传统的I/Q正交调制的QAM发射体系,其EVM及能效比等方面机能体现优胜。该芯片采用了65nm CMOS工艺流片,颠末测试,该电路实现了优胜的3.4%的EVM机能,且仅耗损了659µW功耗到达了26.3pJ/bit的能量效率,同时芯片有源面积仅占0.016妹妹2。

图9:(a)27°C时频率随供电电压的变化(b)0.3V时频率随温度的变化

图10:提出的基在复合相移法的16QAM超低功耗倍频发射机体系

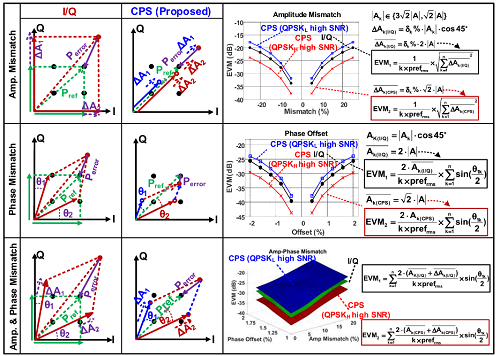

图11:I/Q正交调制 vs CPS复合调制的幅度、相位掉配体系级建模

图12:I/Q正交调制 vs CPS复合调制的幅度、相位掉配体系级建模

参考论文:[1] Zhu Y, Ding W, Lin C C, et al. A Robust Near-Zero Power Wakeup Timer With a Hybrid Reconfigurable FLL Directly Powered by Uncertain Harvested Voltage Down to 0.3 V[C]//2024 IEEE European Solid-State Electronics Research Conference (ESSERC). IEEE, 2024: 520-523.DOI: https://doi.org/10.1109/ESSERC62670.2024.10719527[2] Xu S, Li L, Du Y, et al. A 1.92 nJ/Conv Pulse-Width Locked-Loop Time Domain Readout IC with VCO-Integrator and Pipeline TDC for Wheatstone Bridge Wearable Strain Sensing System[C]//2024 IEEE Asian Solid-State Circuits Conference (A-SSCC). IEEE, 2024: 1-3.DOI: https://doi.org/10.1109/A-SSCC60305.2024.10849316[3] Luo K, Ding W, Lin C C, et al. An Energy-Efficient Composite Phase Shift 16-QAM Frequency Multiplying TX Achieving a 3.4% EVM in 65nm CMOS[C]//2024 IEEE Asian Solid-State Circuits Conference (A-SSCC). IEEE, 2024: 1-3.DOI: https://doi.org/10.1109/A-SSCC60305.2024.10849162-米兰milan