近日,南边科技年夜学深港微电子学院林龙扬课题组于人工智能芯片设计范畴取患上主要冲破,相干研究结果 “A 22nm 29.3TOPS/W End-to-End CIM-Utilization-Aware Accelerator with Reconfigurable 4D-CIM Mapping and Adaptive Feature Reuse for Diverse CNNs and Transformers” 在2025年4月13-16日于美国波士顿进行的专用集成电路集会(IEEE Custom Integrated Circuits Conference,CICC)上陈诉。此项结果同时入选2025年ISSCC的学生科研前瞻单位(Student Research Preview),并于ISSCC集会时期举行了现场芯片演示,揭示了该芯片的优秀机能。该论文的第一作者为深港微电子学院2022级博士生王瑾,通信作者为林龙扬助理传授,第一单元为南边科技年夜学。

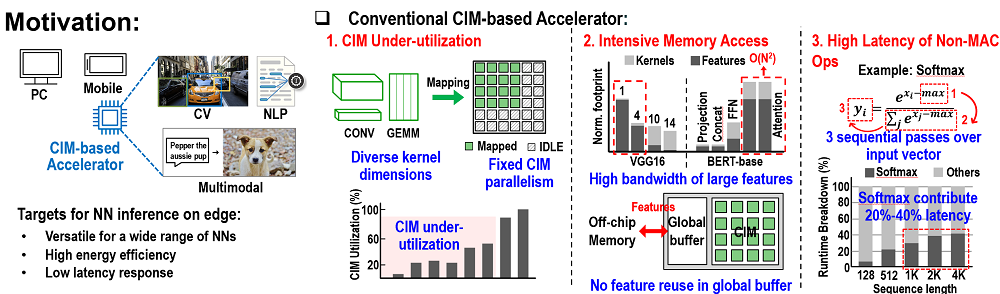

最近几年来,存内计较(Compute-in-Memory,CIM)依附其固有的高并行计较能力及原位数据处置惩罚的怪异上风,于能效比及面积效率方面揭示出显著上风,已经成为人工智能加快范畴最具成长潜力的技能线路之一。然而,面临卷积神经收集(CNN)与Transformer等快速演进的多样化神经收集架构,现有CIM硬件于撑持异构算子时仍面对严重挑战(如图1所示),详细体现为:起首,固定并行度的CIM阵列难以适配多样化算子的计较模式,致使计较资源使用率低下;其次,现有架构缺少针对于差别访存特性的动态数据重用机制,片外数据搬运成为制约机能及能效的重要瓶颈;末了,对于softmax、层归一化等要害向量算子的优化不足,严峻影响端到端推理效率。

图1.面向多种CNN及Transformer收集时所需要的挑战

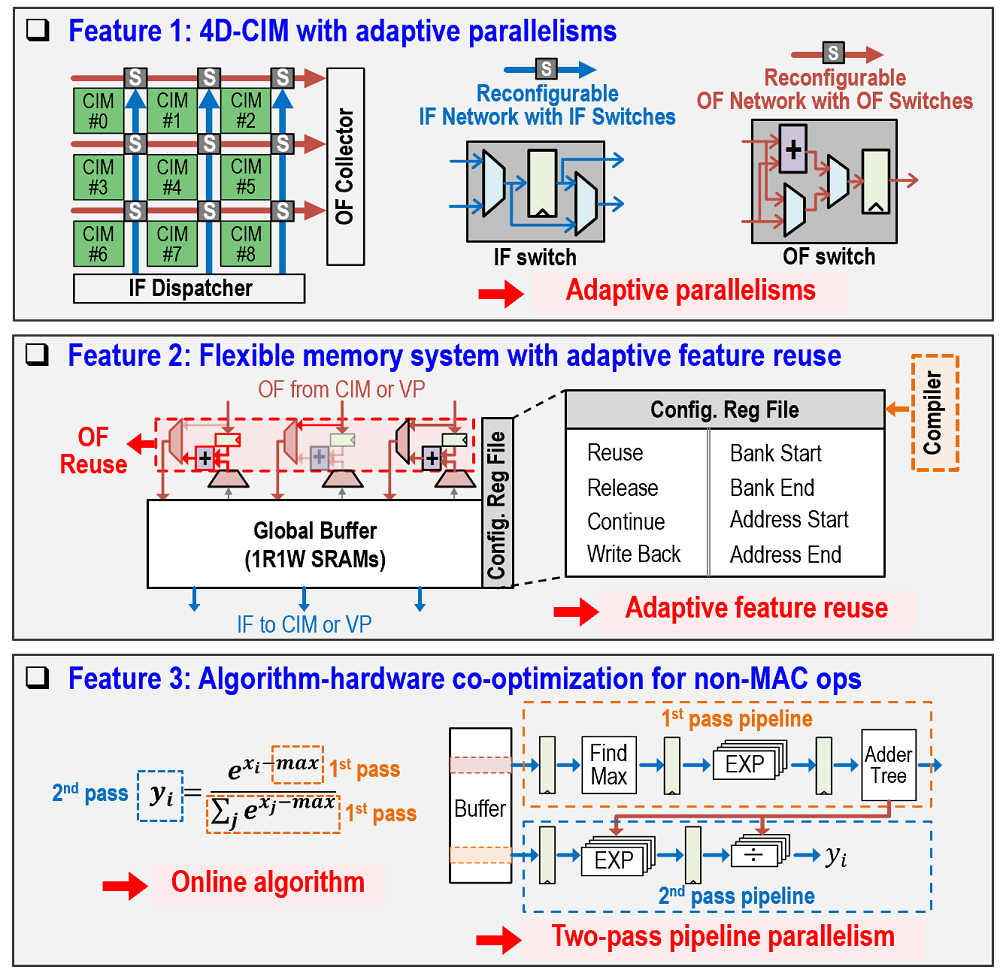

针对于上述挑战,本研究提出了一种立异的动态可重构存算一体加快芯片架构,其焦点立异表现于三个方面(如图2所示):第一,设计了四维可重构CIM处置惩罚单位,经由过程撑持四个维度的动态并行度调解,实现了最高达2.6倍的硬件使用率晋升;第二,构建了编译器引导的智能存储系统,采用全局缓存与寄放器协同的条理化数据复用计谋,经由过程动态配置读写模式,使差别访存特性的算子都能得到最优的数据重用效率;第三,开发了算法-架构协同优化的向量处置惩罚引擎,立异性地采用两阶段于线计较算法替换传统三阶段流程,联合流水线并行化设计,将softmax及层归一化等要害算子的计较通量晋升59%。

图2.针对于上述挑战本文提出的解决方案

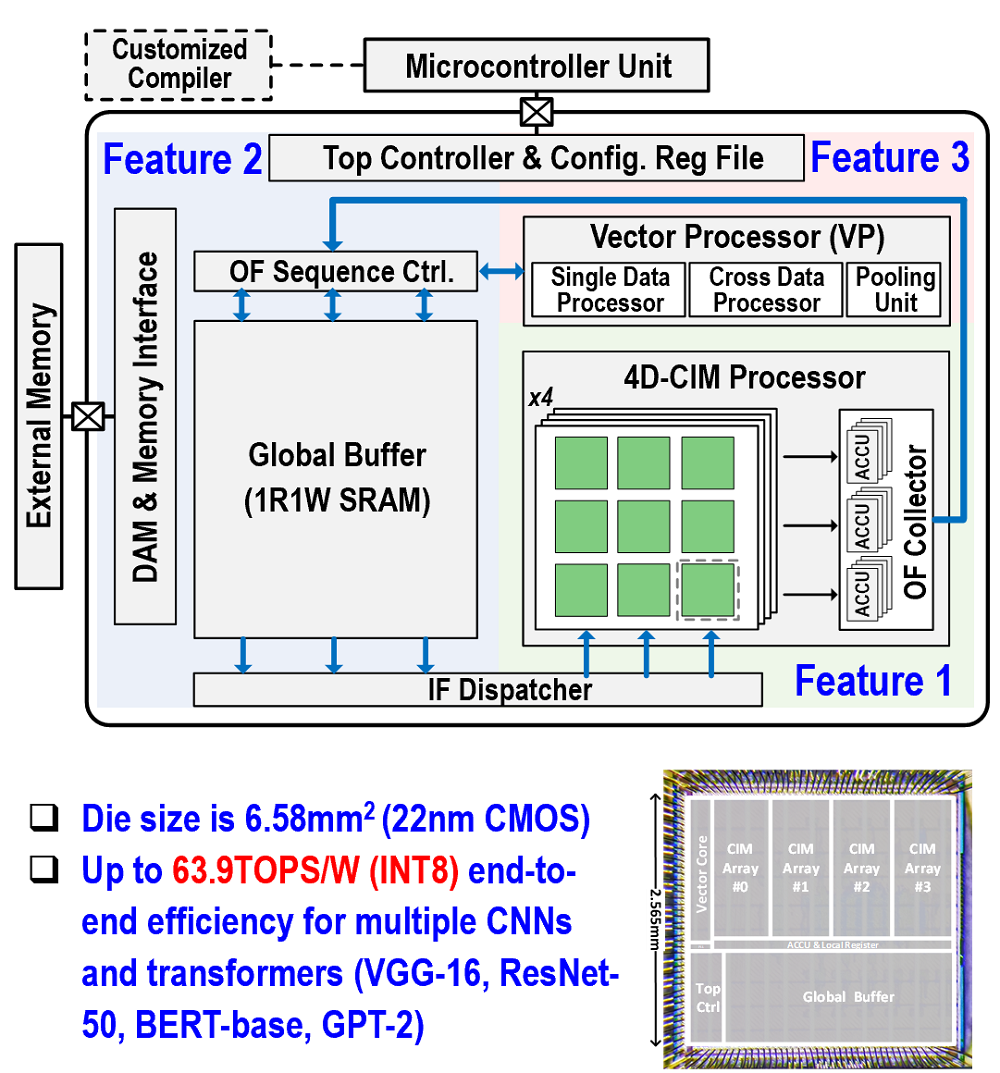

图3展示了基在22nm工艺流片的芯片实现细节和总体架构。实测成果注解,该芯片于运行VGG-1六、ResNet-50及BERT等典型收集时,CIM使用率到达88.9%-99.7%,体系能效最高达29.3TOPS/W,显著优在现有CIM专用加快器方案。这些冲破性结果为构建高效通用的AI加快平台提供了主要的理论依据及工程实践参考。

本研究事情获得了国度天然科学基金、广东省基础与运用基础研究基金、以和存厚科技有限公司的撑持。

图3.基在22nm工艺流片的芯片实现细节和总体架构

论文信息以下:

[1]J. Wang, M. Lou, Z. Yang, R. Peng, H. Li, W. Dong, H. Lyu, Y. Li, J. Li, H. Yu, J. Yooand L. Lin, A 22nm 29.3TOPS/W End-to-End CIM-Utilization-Aware Accelerator with Reconfigurable 4D-CIM Mapping and Adaptive Feature Reuse for Diverse CNNs and Transformers , 2025 IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 2025.

关在CICC

IEEE专用集成电路集会(CICC)是集成电路设计范畴的顶级集会之一,由IEEE固态电路协会(Solid-State Circuits Society)主理,IEEE 电子器件协会(Electron Devices Society)协办,是集成电路设计新技能会商以和与偕行、作者及行业专家成立接洽的极具影响力的集会。CICC集会时期将展示初次发表的具备原创性的技能结果,以和能解决现实工程问题的立异电路技能,触及模仿电路技能、生物医疗电路技能与运用、数据转换器、数字电路与片上体系、人工智能处置惩罚器、电源治理、硬件安全、无线与射频技能、有线与光通讯技能等集成电路范畴的前沿研究标的目的。

-米兰milan