近日,南边科技年夜学深港微电子学院陈凯传授课题组于用在量子计较数据丈量与节制的低温CMOS器件的阈值电压建模范畴取患上主要进展,相干结果以论文“Characterizationsand Framework Modeling of Bulk MOSFET Threshold Voltage Based on a Physical Charge-Based Model Down to 4 K”[1]被国际顶级学术集会——2024年欧洲固态电子研究集会(European Solid-State Electronics Research Conference, ESSERC 2024)接管。陈凯传授课题组2021级硕士研究生苏浩、2022级硕士研究生谢云枫是论文的配合第一作者,陈凯传授为论文的通信作者,南边科技年夜学深港微电子学院为论文的第一单元。该结果获得了深圳市南山戋戋校共建微电子学院“5G”前沿项目第2、三两期资金的撑持。

ESSERC由此前欧洲固态器件集会(ESSDERC)及欧洲固态电路集会(ESSCIRC)这两个部门构成,本年初次将两个集会归并为ESSERC,规划在9月于比利时的布鲁日召开。

当前,几种具备潜力的量子计较机的量子比特(qubit)需要事情于1 K如下的mK低温情况下,以维持量子比特的相关性。相干的测控CMOS电路今朝也被置在4 K摆布的温度。而于将来,为了提高集成度,并应答将来快速增多的量子比特数量,量子读取及节制的CMOS电路有可能需要与量子比特数据层一路配合放置于mK的温区中。而迄今为止的国际财产尺度模子如BSIM3v3/BSIM4,其温度设定为一样平常CMOS芯片所运用的靠近室温情况。是以,于低至4 K以致mK的低温CMOS(Cryo-CMOS)情况下,器件和电路会有何异在常温的体现,需要被研究并精准地建模。

阈值电压作为几个描写MOSFET的基本参数之一,其超低温的表征和机理于近几年国际上的一些论文中被说起并举行了必然水平的研究,但基在更深条理的(如于低温下的载流子冻结及MOS晶体管界面态效应等物理机理)将阈值电压的超低温表征、器件尺寸微缩及偏置状况所带来的二阶效应相联合举行体系性的研究,于国际上仍旧存于缺掉。

基在本团队此前已经于IEEE JEDS期刊发表的一个新提出的基在电荷的阈值电压超低温物理解析模子[2][3],研究团队对于阈值电压于器件尺寸微缩及偏置状况这两个维度,对于短沟道效应、窄沟道效应、漏端引入的势垒降低效应(DIBL)及体效应举行了体系性的超低温建模,成立了一个框架性的阈值电压超低温模子;同时,于40纳米及180纳米的Bulk CMOS工艺节点设计并举行了器件测试矩阵的流片,完成为了从300 K到低至4 K超低温的器件电学机能测试。该阈值电压框架性模子将此条件出的超低温物理模子,与国际财产尺度模子BSIM于低温下的修改相联合,将模子合用规模扩大到了差别尺寸的器件于低至4 K的低温下的更繁杂偏置状况,并切确地拟合了测试数据,揭示了新模子凸起的物理意义及可扩大性(scalability)。

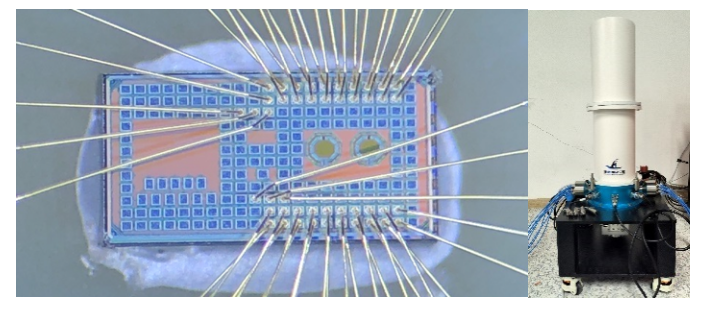

图1由晶圆代工半导体厂家加工和绑线的40纳米Bulk CMOS工艺MOSFET器件样本,以和测试样品的超低温真空腔。

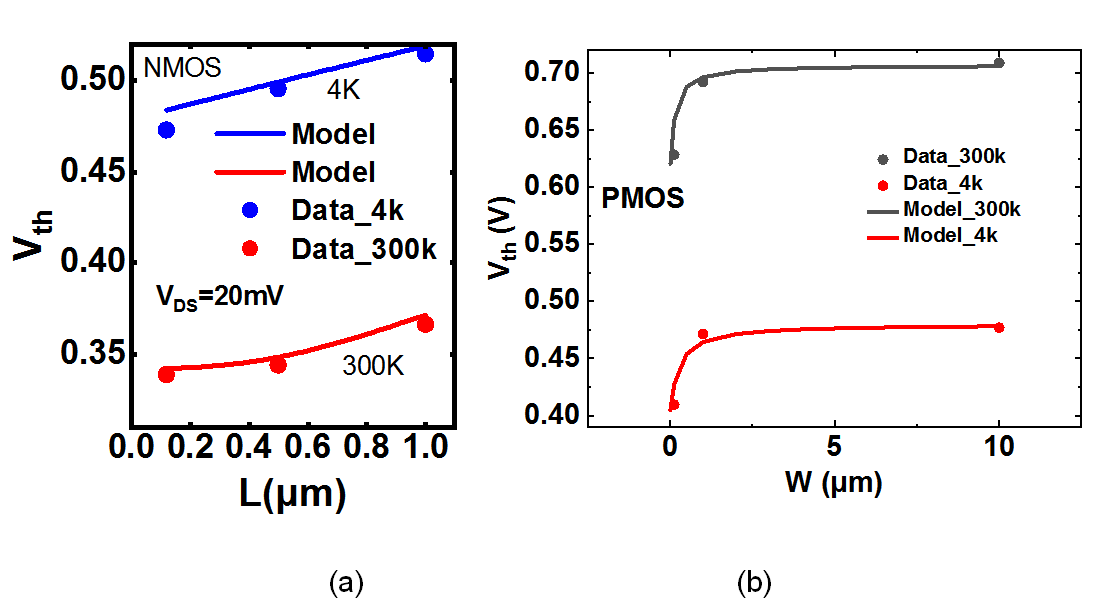

图2常温与4 K的超低温阈值电压尺寸微缩效应:(a)对于沟道长度低至120纳米、沟道宽度为1微米的NMOS器件阈值电压-沟道长度微缩测试成果与模子;(b)对于沟道长度为1微米、沟道宽度低至120纳米的PMOS器件阈值电压-沟道宽度微缩测试成果与模子。

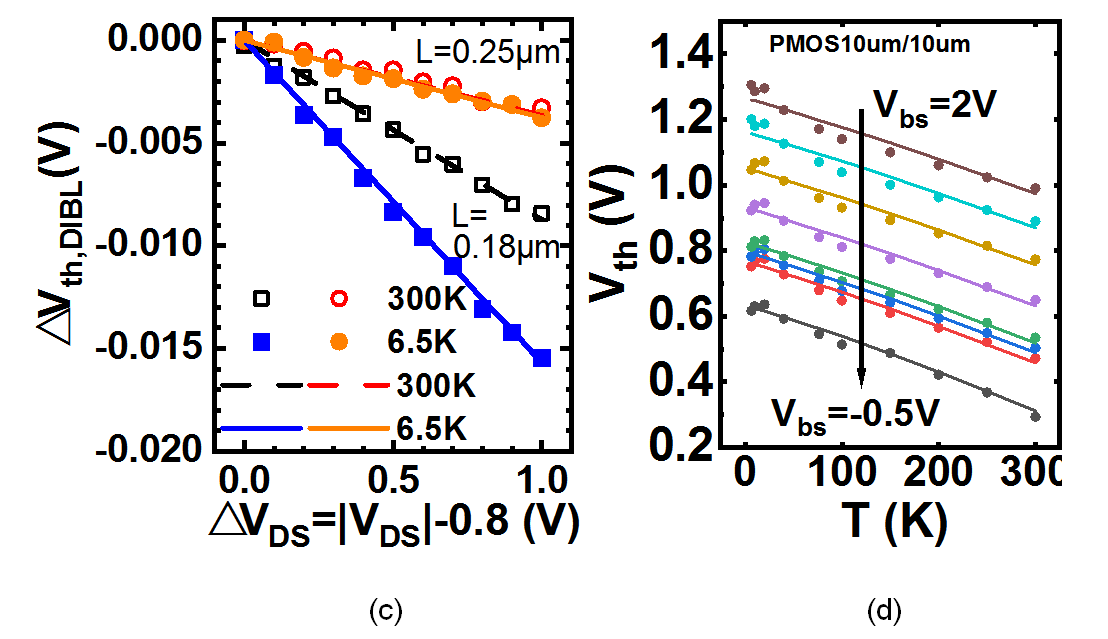

图3低至4 K的超低温阈值电压偏置效应:(a)对于沟道长度为250纳米及180纳米、沟道宽度为1微米的PMOS器件举行的DIBL效应测试成果与模子;(b)对于沟道长宽均为10微米的PMOS器件举行的超低温体效应测试成果与模子。

陈凯传授课题组的重要研究标的目的为面向量子计较的超低温CMOS器件物理建模与电路研究,研究团队于从室温到低至10 mK的超低温范畴针对于MOSFET器件的物理建模取患了一系列进展,于IEEE JEDS [3]等知名期刊与学术集会均发表了论文。此中,另外一项低至10 mK的超低温MOSFET阈值电压及要害模仿参数的建模事情,也在近期于IJNM期刊发表了论文[4]。课题组内的2021级硕士研究生苏浩得到了2024年南边科技年夜黉舍级优异卒业研究生表扬,以后将会于澳门年夜学攻读博士学位;2022级硕士研究生谢云枫主持、介入了课题组内屡次器件测试电路及数模混淆电路流片项目。

参考文献:

[1] Hao Su, Yunfeng Xie et al.,“Characterizationsand Framework Modeling of Bulk MOSFET Threshold Voltage Based on a Physical Charge-Based Model Down to 4 K,”Accepted byEuropean Solid-State Electronics Research Conference, 2024.

[2]Hao Su et al., Characterization and Threshold Voltage Modeling of Bulk P- MOSFETs Down to 10 mK for Cryogenic CMOS Design, inthe 7th International MOS-AK Workshop, Nanjing, Aug. 2023, pp. 7–9.

[3]HaoSu et al., “A Physical Charge-Based Analytical Threshold Voltage Model for Cryogenic CMOS Design,”IEEE Journal of the Electron Devices Society, pp. 1–1, 2024, doi:10.1109/JEDS.2024.3359664.

[4] HaoSu, Yiyuan Cai et al., “Investigation of Long Channel Bulk MOSFETs Threshold Voltage Model Down to 10 mK and Key Analog Parameters at 4 K,”International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, 2024, doi:10.1002/jnm.3258.

-米兰milan